読む前に覚えておきたい用語

インターコネクト(Interconnect)

インターコネクトとは相互接続を意味し、主に機器内のチップ間を接続して命令やデータのやりとりを可能とする伝送路のことを指す。コンピュータのインターコネクトは、古くはISA Bus、EISA、VL Busなどのローカルバスに始まり、MacではNuBusが、PCではPCI Busなどの汎用バスへと発展していった。

PCI(Peripheral Component Interconnect)

CPUアーキテクチャに依存しない高速バスとして、PCI-SIGによって1992年に策定された汎用インターコネクト規格。MacでもそれまでのNuBusに代わって、1995年リリースのPower Mac 9500/8500シリーズからPCI 2.0が採用され高性能化に貢献した。

PCI Express

PCI規格を策定したPCI-SIGによって2002年に策定されたシリアル伝送のインターコネクト規格。パラレル方式のPCIバスの欠点を補い、より大幅な高速化を実現するための新規格としてインテルの3GIO(3rd. Generation I/O)をベースに開発された。ちなみに、AGPの代わりにビデオカードのインターフェイスとしても利用される。

I/Oの高速化とPCIe Gen3の制約

現在のMacのインターコネクトには、例外なくPCIエクスプレス(以下、PCIe)が採用されている。PCIeは2005年登場の第2世代Power Mac G5で初めて採用され、インテルMacはすべてPCIeベースのシステムアーキテクチャを採用している。

PCIeは何度かのバージョンアップによって高速化が行われ、現在普及しているのは2010年11月に制定されたPCIe Gen3だ。インテルプロセッサでは第3世代Coreプロセッサ「アイビーブリッジ(Ivy Bridge)」以降に採用されている(Sandy Bridge以前はGen2)。PCIe Gen3では1レーンあたりの転送速度は物理層レベルで8Gbpsで、インテルプロセッサを搭載したコンピュータではプロセッサタイプによって提供されるPCIeレーン数が異なる。

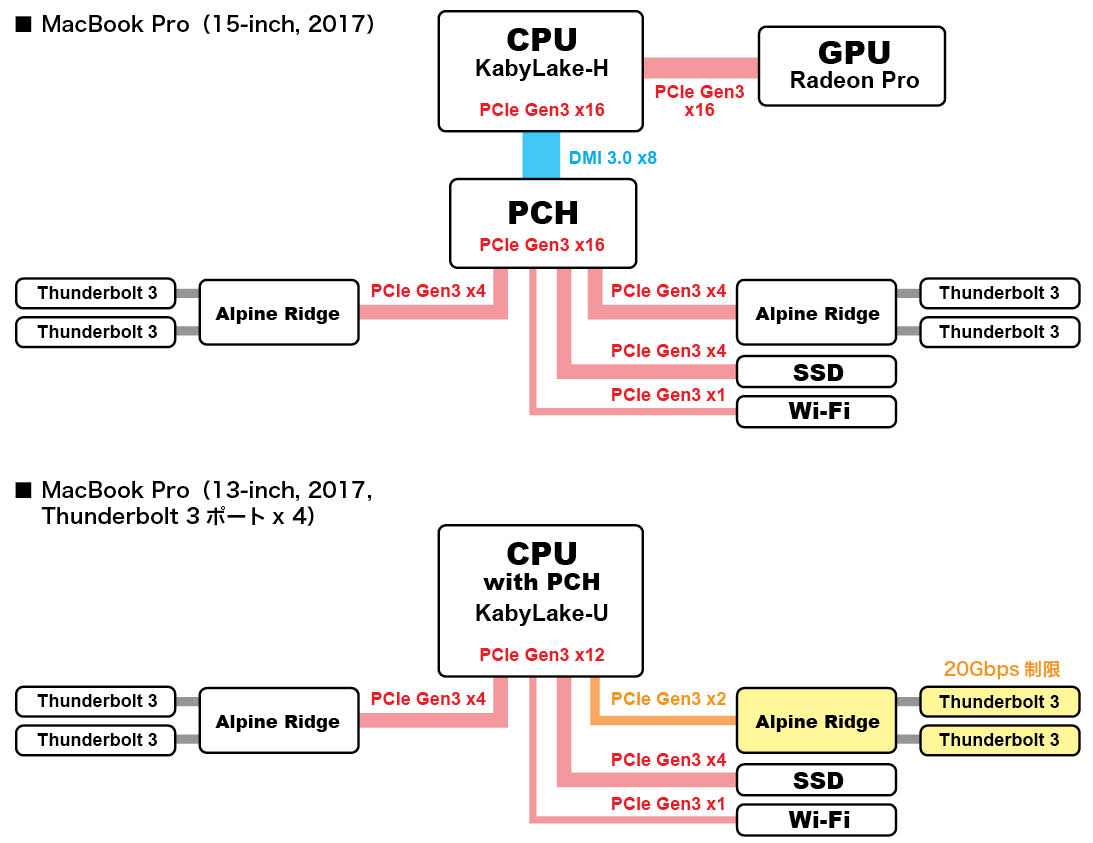

たとえば、MacBookプロ13インチモデルに採用されている第7世代Core Uプロセッサ(KabyLake U)の場合、統合されるPCHが提供するPCIe Gen3のレーン数は合計12レーンで、これらは4レーン、2レーン、1レーンのいずれかの構成でのみ利用できる。これに対して、同モデルに搭載されているインターフェイスはSSD用のNVMeに4レーン、Wi-Fiに1レーン、サンダーボルト3には2ポートあたり4レーン必要なので、タッチバーとタッチIDを備える4ポートモデルではCore Uプロセッサの提供するPCIeのレーン数が1レーン不足することになる。これがタッチバーとタッチID付きモデルの右側のサンダーボルト3ポートが最大20Gbpsに制限されている理由だ。つまり、右側のポートには、サンダーボルト3コントローラである「Alpine Ridge」にPCIeが2レーンしか接続されていないのである。

一方で、MacBookプロ15インチモデルが採用する第7世代Core Hプロセッサ(KabyLake H)では、PCHが別チップで搭載されていることもあって、PCIe Gen3は16レーン(ディスクリートGPU専用)+16レーン(I/O用)の合計32レーンが提供されており、4つのサンダーボルト3ポートすべてで40Gbpsのフルスピードが実現できる。

しかし、これも余裕がある状態ではなく今後インターフェイスの高速化やポート数の増強を進めればPCIeの帯域が不足することは明白だ。つまり、現在のMacはインテルプロセッサが提供するPCIe帯域をほぼ使い切った状態で、これ以上のインターフェイスの高速化にはPCIeの進化が必要不可欠な状況にある。

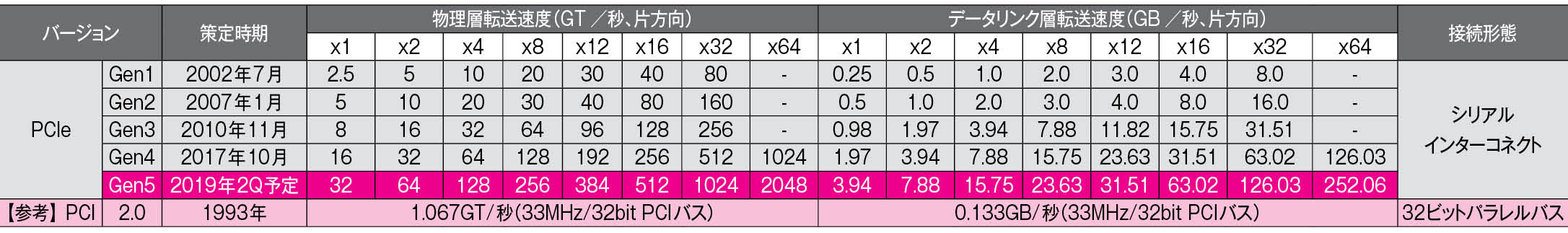

PCIeの伝送速度一覧

PCIeおよびPCIバスの各バーションと、レーン数あたりの転送速度。PCIeはバージョンアップの都度、レーンあたりの転送速度が2倍に向上してきた。さらにGen4からは最大レーン数が64レーンに拡張され、より高速なインターフェイスにも対応できる。

MacBook Proのブロックダイアグラム

13インチモデルではCore Uプロセッサが提供するPCIe Gen3のレーン数が、各インターフェイスが求める合計レーン数に対して不足していることがわかる。

左右でポートの速度が違う!?

MacBook Pro(13-inch, 2017, Thunderbolt 3ポートx 4)モデルでは、右側の2ポートの転送速度が最大20Gbpsという制約がある。これは搭載するCore UプロセッサのPCIe Gen3のレーン数が不足したためだ。【URL】https://www.apple.com/jp/

レーン数を増やさず速度を倍増するGen4

そこで期待されるのが、昨年10月にリリースされたPCIe Gen4だ。PCIe Gen4は従来のGen3に対して1レーンあたりの帯域を2倍に引き上げ、物理層で最大16Gbpsの伝送速度を実現する。つまり、システム全体の転送速度を2倍に向上させることができる。問題は、それがいつインテルプロセッサに採用されるかに掛かっている。

PCIe Gen4はすでにIPデザインベンダーから14nmまたは10nmプロセス向けのIPがリリースされており、IBMが昨年12月より生産を開始した同社の新プロセッサ「Power 9」では、PCIe Gen4を48レーン採用し片方向96GB/秒、双方向で192GB/秒という広帯域接続を可能としている。

インテルも10nmプロセスで製造を予定している、次世代FPGA(Field Programmable Gate Array)では、広帯域メモリのHBMと共にPCIe Gen4のサポートを表明していることから、すでに同社では10nmプロセス向けのPCIe Gen4のIPデザインを用意していると考えられる。従って早ければ、2018年内に10nmプロセスで生産が開始される予定の「キャノンレイク(Cannon Lake)」でPCIe Gen4が採用されることが期待される。

ただし、同時に周辺チップのGen4対応も必要だ。現在サンダーボルト3にはインテルのAlpine RidgeがPCIe Gen3で4レーン接続で使用されているが、Gen4ではわずか2レーンで従来と同じ転送速度を実現できる。一方、SSDに使われるNVMeでは、4レーン接続のままでGen4対応になると推測され、その転送速度は最大理論値で約8GB/秒(64Gbps)と現在の2倍に向上することが期待される。

iMacプロにMacとして初めて採用された10GビットLANも、PCIe Gen4への対応がメリットとなるデバイスの1つだ。現在のGen3では2レーン接続となっている10GビットLANコントローラだが、Gen4対応チップでは1レーン接続でも10Gbpsの帯域をサポートできるようになるためだ。

このように、PCIe Gen4への移行が進めば、各半導体ベンダーからリリースされるさまざまなインターフェイスチップも、特に高速伝送を必要とするものから優先的に同規格への対応を進めてくると推測される。

PCIe Gen4に対応したIBM POWER 9

2017年12月にIBMからリリースされたディープラーニングワークロード向けサーバ「IBM Power System AC922」には、最新のPCIe Gen4(48レーン)を業界に先駆けて採用した「POWER 9」プロセッサが搭載されている。【URL】https://www-03.ibm.com/

PCIe Gen5の登場は2019年以降か

昨年ようやく規格策定が終了したばかりのPCIe Gen4だが、すでに次世代規格であるPCIe Gen5の標準化作業も始まっている。昨年10月のGen4リリース時点の予定では、2019年第2四半期の公開を目指していると発表されている。Gen5では1レーンあたりの伝送速度をGen4の2倍、Gen3の4倍に引き上げ、物理層でレーンあたり最大32Gbpsの伝送速度を実現する予定だ。

システムのバックボーンを担うインターコネクトとして、PCIeは幾度かのバージョンアップにより高速化を成し遂げてきた。そしてすでにPCIeはパソコンやサーバなどのコンピュータのみならず、iPadやiPhoneなどの携帯端末の中核(SoC内部のコアIP)にも採用されており、あらゆるデバイスを構成するうえで欠かせないベース技術となっている。

最近では、統合されたGPUやイメージプロセッサ、ニューラルエンジンなどとの間でより広帯域な接続が求められており、インターコネクトの高速化への要求が高まっている。システム全体の性能に大きな影響を及ぼすインターコネクトの進化は、今後も決して留まることはないだろう。

今井 隆

IT機器の設計歴30年を越えるハードウェアエンジニア。1983年にリリースされたLisaの虜になり、ハードウェア解析にのめり込む。