高速化の歴史とその限界

1997年に登場したPower Macintosh G3シリーズで初めてメインメモリとして採用されたSDRAM(Synchronous DRAM)は、それまでCPUやシステムバスとは非同期で動作していたDRAMを改良し、アクセスのパイプライン化とクロック同期入出力によってサイクルタイムを大幅に高速化した画期的なDRAMだった。SDRAMはその動作クロックを向上させることで高速化が可能だが、200MHz以上のクロック伝送はその精度やノイズ面で課題が多いため、クロックエッジの両サイドを使用することで倍速のデータ転送を実現するDDR(Double Data Rate)-SDRAMが開発された。

その後もクロックの4倍速で動作するDDR2-SDRAM、8倍速動作のDDR3-SDRAMへと移行し、現在はiMacなど一部のモデルで16倍速のDDR4-SDRAMが採用されている。その転送速度はDDR3-SDRAM(1600MHz動作)の場合、メモリチップ単体(8ビット)では1.6GB/秒、DIMM構成(64ビット)では12・8GB/秒となる。インテルのコア(Core)iプロセッサはこれを同時に2チャンネルアクセスするデュアルチャンネルアクセスにより25・6GB/秒、さらにジオン(Xeon)プロセッサではトリプルチャンネル(38・4GB/秒)やクアッドチャンネル(51・2GB/秒)を採用し、データベース処理等のメモリ依存度の高い処理を高速化している。

だが、その速度はCPUにとって充分ではなく、いつの時代もメインメモリはCPUにとって大きなボトルネックだった。現在のプロセッサではCPUとその内蔵一次キャッシュメモリ(L1)とのバンド幅(最大転送速度)は1TB/秒以上に達しており、メインメモリのバンド幅との解離は二桁に及んでいる。このため、最近のインテルプロセッサでは例外なくL1、L2、LL(ラストレベル)の3階層のキャッシュメモリを間に挟むことで、その速度差の影響を低減しているのが実状だ。

iMacなどに採用されているDDR4-SDRAM SO-DIMM。これは8GBの容量で、4GビットのDDR4-SDRAMチップが両面に8個ずつ、計16個搭載されている。コンタクト(接点)は260ピンと細かく、配線パターンも複雑になっている。

現在のCPUのメモリシステムは、よりCPUコアに近い部分からL1(一次キャッシュ)、L2(二次キャッシュ)、LL(ラストレベルキャッシュ)の3層のキャッシュメモリを挟むことで、メインメモリのアクセス速度の遅さをカバーしている。

GPUが牽引するメモリ高速化

このようにCPUにとってメインメモリの速度不足は長年の課題となっているが、CPU以上に深刻な状態なのがグラフィックス処理を担うGPUのメモリだ。GPUはCPUとは異なり、膨大な数の演算コアを並列動作させることで高速処理を実現する並列処理(SIMD)型コプロセッサである。数十~数千個もの演算コアが並列動作し、処理の入出力を大量のメモリ空間に対して同時に行うため、非常にメモリ帯域への依存度が高いプロセッサといえる。このためGPUは常にCPUより高速なメモリを採用してきた歴史があり、その技術がCPUのメモリへとフィードバックされてきた。従ってGPU用メモリ(ビデオメモリ)の進化を見れば、CPU用メモリ(メインメモリ)の行く末をある程度予測することが可能だ。

現在のGPUに採用されているビデオメモリはGDDR5-SDRAMが主流で、その動作速度は5~7GHz相当と非常に高速だ。ハイエンドクラスのGPUの場合、このGDDR5-SDRAMを384ビットまたは512ビット接続とすることで、240GB/秒または320GB/秒(5GHz動作時)と極めて高いバンド幅を確保しており、文字どおりCPU用メモリとはそのバンド幅が「桁違い」である。

だが、近い将来、CPUもDDR 5-SDRAMが主流になるのか、といえばそれは難しいだろう。GDDR5が5GHzを超える速度を実現しているのは、GPUと最短距離でピアトゥピア(1対1)接続される、という条件が満たされているためだ。その点でDIMMのようなモジュール構造で搭載され、メモリバスに複数のDIMMを接続されるメインメモリのような利用形態では8GHz動作はおろか4GHz動作でも厳しい。当初DDR4-SDRAMの規格化にあたっては複数DIMMの接続はサポートされない予定だったが、最終的に2スロットまで速度条件付きで認められた経緯がある。それほどシビアな状態に追い込まれている証拠であり、現状のメモリモジュール構造のままでは次の世代(DDR5)への移行が困難であることを示している。

新しい三次元実装技術TSV

メモリへのアクセス速度を向上させる方法は2つある。1つはスピード(動作速度)の向上で従来のメモリはこの方法で高速化する方法を採ってきた。同じ道路でもクルマの速度を上げると荷物や人を多く運べるが、これはデータも同じだ。もう1つはバス幅を拡張する方法。クルマの速度を上げずに道路のレーンを増やすアプローチだ。

しかし、この方法には大きな問題がある。すでに64本や128本もあるメモリのデータバスをさらに拡張するとなると、メモリチップのピン数、CPUやGPUのピン数、それを実装する基板の配線数が大幅に増えることになるためだ。特に、現状でも128~512本のメモリバスを接続しているGPUは、すでにそのピン数が数千本に及んでおり、基板設計も非常に難しくなってきている。これをそのまま2倍、4倍のバス幅に拡張することは現実的に不可能と思われる。

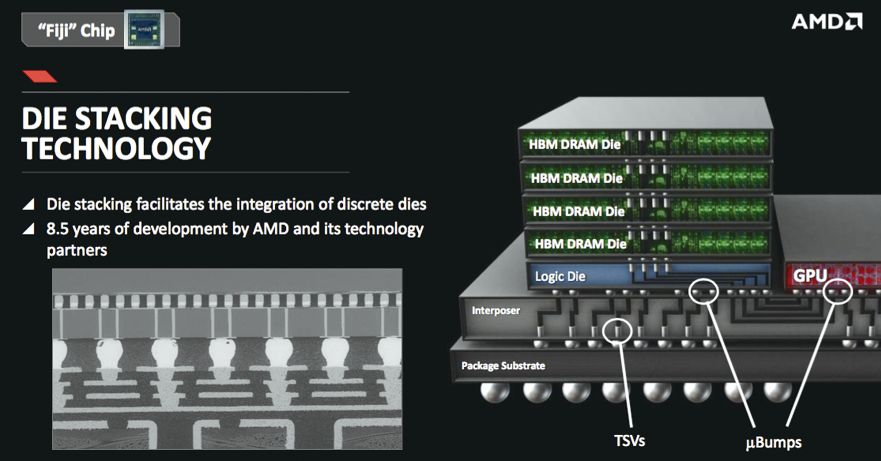

そこで考案されたのが、マイクロバンプを用いた新しい実装技術「TSV(Trough Silicon Via=シリコン貫通ビア)」である。シリコンダイを縦に重ねて積層する技術自体は古くからあり、通常はダイと外部ピン間をワイヤボンディングで接続する方法が採られる。これに対してTSVはダイ自体に上下に貫通した微細な端子(マイクロバンプ)を設け、これを積層することで複数のシリコンダイをワイヤなしで接続することを可能にする。

この技術を使って作られたメモリチップがHBM(High Bandwidth Memory)だ。HBMでは1024本のメモリバスを有し、これを1~2GHzの速度で動作させることで、ワンチップで128~256GB/秒の伝送速度を実現する。HBMを初採用したのがAMDの「Radeon R9 Fury」で、1GHz動作のHBMを4個搭載し、GPUとメモリ間を4・096ビットものデータ幅で接続することで512GB/秒という高速伝送を実現した。なお、従来の「Radeon R9 290X」では5GHz動作のGDDR5-SDRAMを搭載、512ビットのメモリバスで接続し、転送速度は320GB/秒だった。

HBMはさらに改良が続けられ、今年に入ってより高性能化と汎用化を実現したHBM2規格の製品が登場した。HBM2は今年4月にそのアーキティクチャが公開されたnVIDIAの次世代GPU「パスカル(Pascal)」に採用される予定で、従来のHBMが4個で512GB/秒であったのに対して、パスカルではHBM2を4個搭載して720GB/秒を実現する見通しだ。さらにHBM2では今後単体で250GB/秒、4個で1GB/秒まで計画されている。

HBMを業界に先駆けて採用したAMDのGPU「Radeon R9 FURY(Fiji)」。GPUパッケージ上に1024ビット接続のHBM-DRAMを4個搭載し、合計4096ビットものメモリバス幅を確保することでビデオメモリのバンド幅を拡大している(*1)。

従来の積層メモリチップでは、パッケージ内に複数(2~16枚)のメモリダイ(シリコン)を重ねメモリダイとインタポーザ間をワイヤで接続していたが、HBMはワイヤに代わってTSV(シリコン貫通ビア)を用いて配線する。

TSV(シリコン貫通ビア)を使うことで、DRAMを複数積層して実装することができるようになる。GPUとはインターポーザーと呼ばれる中間基板を介して接続されるが、将来的にはGPUやCPUにDRAMを積層することも可能だ(*1)。

HBM/HBM2の採用がもたらすのは高速化だけではない。メモリチップがGPUパッケージ上に搭載されることで、ビデオカード上のメモリチップとそこまでの配線が不要となり、基板面積を大幅に縮小できる(*1)。

AMDの従来のビデオカードに比べると、HBMを採用したRadeon R9 NANOのサイズは大幅に小型化されている。GPUにビデオメモリが統合されたことによって、従来GDDR5-SDRAMとそこへの配線に占領されていた基板面積が解放された形だ(※1)。※1 参照:SEMICON TAIWAN http://www.semicontaiwan.org/

HBMのメリットとデメリット

このようにHBM/HBM2は、従来のメモリとは比べものにならないサイズで従来と同等以上のアクセス速度をGPUにもたらした。だが、HBM/HBM2が直ちにCPUのメモリに採用されるかといえば、それはまだ少し先の話になりそうだ。というのも従来のCPUのメモリは拡張性が求められたため、DIMMやSO-DIMMなどのメモリモジュール構造が採用されていた。

これに対してHBM/HBM2ではTSVという特殊な構造を採用している関係で、CPUまたはCPUを搭載したサブスレート上にメモリを直接実装する必要がある。このことはCPUに直接メモリが搭載されることを意味しており、従来のようにユーザが自由にメモリを単体で拡張(交換または追加)できなくなる(ただしHBM/HBM2を搭載しつつ、外部メモリインターフェイスを残すという方法もある)。

しかし、現実にはMacBookエアやMacBookプロなどのほとんどのモデルでメインメモリはロジックボードに直接実装されており、ユーザがこれを拡張する余地はない。従って今後インテルプロセッサがHBM/HBM2に移行しても大きなデメリットにはならず、逆にロジックボードの大幅な小型軽量化が可能となるメリットがある。

また、iOSデバイスではすでに「アップル A4」の世代からSoC内部にメインメモリ(SDRAM)を取り込んでいるが、今後HBM2の搭載によってメモリの大幅な高速化が可能になる。特に「アップル A9X」などのGPU強化プロセッサ(広帯域化のためSDRAMを外付けにしている)ではそのメリットが大きく、今後のiPad向けSoCにはHBM2が採用される可能性も充分考えられる。

HBM/HBM2の当面の課題は、その構造から来る部品および実装コストの高さだ。しかし今後順調に普及が進めば、そのデメリットを高速化などのメリットが上回る可能性を充分秘めている。特に小型軽量化の要求の厳しいスマートフォンやタブレットにHBM/HBM2の採用が進めば、その普及と低価格化が一気に加速される可能性が高い。今後のメモリの進化の方向性はこれらモバイルデバイスが大きな鍵を握っているといえそうだ。

【News Eye】

nVIDIAは次世代GPUのパスカルで採用するメモリに関して、HBM2とGDDR5Xの2種類をサポートすると発表した。GDDR5XはGDDR5の改良版で、10GHz相当の動作速度を実現し、CUDAコア数は2560個、演算性能は9TFLOPSに達するという。

【News Eye】

インテルプロセッサの一部が搭載するeDRAMは容量が128MBで、転送速度は50GB/秒程度とされている。CPUコアから見ると、eDRAMはLLキャッシュとメインメモリの間に入るL4キャッシュとして機能している。