カギとなるのは分割点の最適化、ダイ分割によるメリットとは

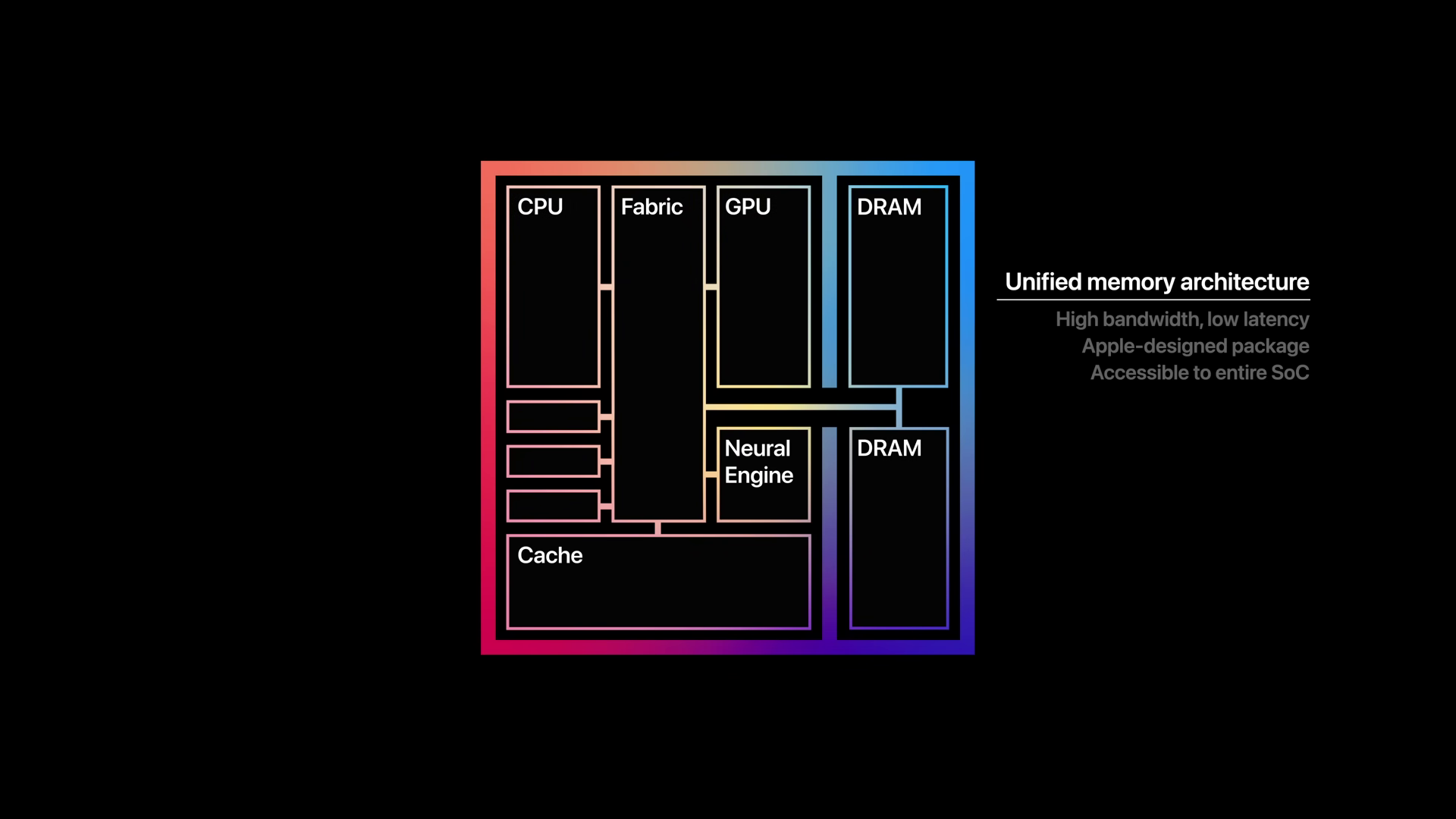

筆者がもしAppleシリコンがダイを2つに分割するとしたら、Intel風の表記で言うと「GPUを統合したCompute Tile」と「Platform Controler Tile」の2つだ。前者にはCPU、GPU、Neural Engineとファブリック、メモリコントローラが含まれる。

一方後者にはUSBやThunderbolt、PCIe、DSP、ISP、Network、Secure Enclove、Sensor HUBなどが含まれる。ただし、メモリコントローラのPHY(物理層)とカメラ周りの処理系(どちらもそこそこ広帯域だが場所を取る)をどちらに置くのが適切かは悩ましいところだ。

画像上:Apple

画像下:Apple

クレジット:Apple

シリコンをプロセッサ系とインターフェイス系に分離することで、前者をN2などの最先端プロセス、後者をN6などの成熟プロセスで製造することでダイコスト全体を削減し、パッケージの複雑さにともなうコストアップを相殺する。これによって最先端プロセスを用いるダイ面積を減らし、1枚のシリコンウエハーから採れるダイの数が増えて単価を下げることができる。

これを実際のAppleシリコンに当てはめて考えてみよう。iPhone 17シリーズに採用されているAppleシリコン、A19とA19 Proは実はダイが異なる(機能無効化による同一ダイの使い回しではない)。A19 ProはA19よりもGPUコアが1個多く、さらにCPUのLLC(Last Level Cache)容量が2倍ある。このためA19 ProのダイサイズはA19よりも約20%大きい。つまり、Appleは現時点においても、機能がほぼ同一ながら性能が異なる2種類のシリコンを作り分けているのだ。

ダイ分離によってプロセッサダイを2種類作り、インターフェイスダイは共用する。しかも最先端プロセスのプロセッサダイを今以上に小型化できるので、コストメリットが大きい。また、インタフェイスダイは複数世代のiPhoneで使い回せる可能性が高いのもメリットだ。さらに、機能が物理的に分離されるため、設計の難易度やデバックに要する時間も低減される。Appleにとっては、この点がもっともWMCMへの投資効果が高い可能性がある。

これはMacやiPadに搭載されるMシリーズも同様だ。大きくなり続けるダイサイズを分割することで、最先端プロセスを要求するプロセッサダイを縮小することでコストを低減し、歩留まりを向上させることができる。

さらに、インターフェイスダイは、MacBookシリーズのようなノート型と、Mac miniやMac Studioのようなデスクトップ型の2種類を作ることで、それぞれのMacが求める外部仕様に最適化しつつ、複数世代で使い回すことが可能になるのだ。

実は、Appleはすでに“WMCM的アプローチ”を試していた。最後にその伏線を振り返ってみたい。