※本記事は『Mac Fan』2023年8月号に掲載されたものです。

– 読む前に覚えておきたい用語-

| FET | プロセスルール | チャネル |

|---|---|---|

| トランジスタの一種でユニポーラトランジスタとも呼ばれる。一般的なバイポーラトランジスタが電流によって制御されるのに対して、FETは電圧(電界)によって制御される特徴があり、プロセッサチップなどに適している。 | 半導体チップの製造プロセスにおいてその加工精度を示す指標で、プロセスノードとも呼ばれる。その数値「nm」はプレーナFETではゲート長を示していたが、FinFET以降ではプレーナFET換算の指標として表記されることが多い。 | FETはソースとドレインの間の電流をゲート電圧によって制御するが、このゲートに接したソースとドレイン間の電子の通り道をチャネルと呼ぶ。チャネルの面積を広くすることでFETの性能(速度)を高めることができる。 |

次世代Appleシリコンを支える「3nmプロセス」とは?

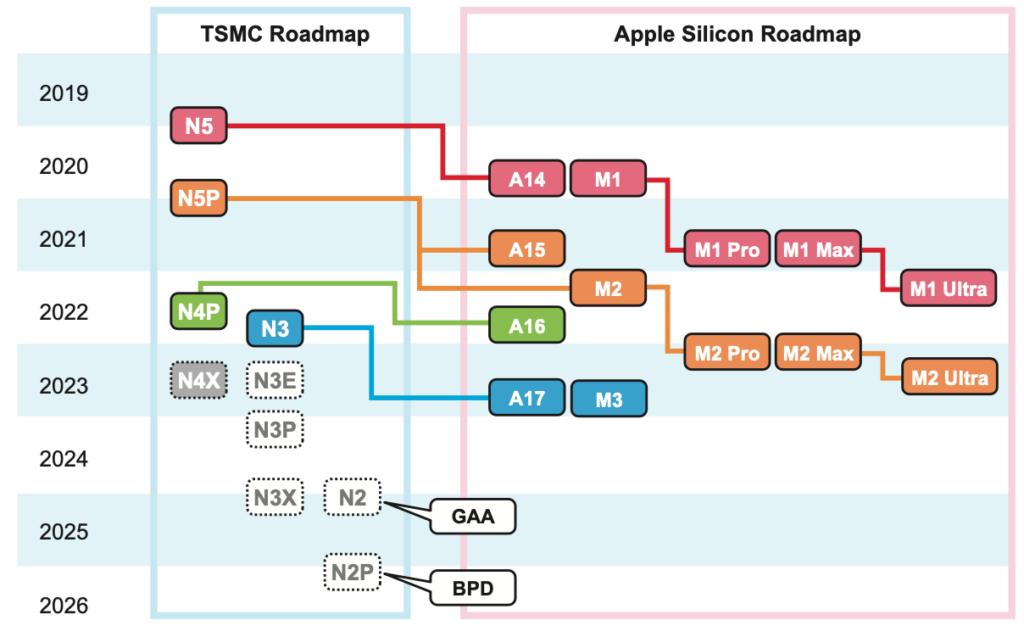

2020年にリリースされたはじめてのMac用Appleシリコン「M1」は、「世界最速のCPUコア」と称される高い演算性能と、その圧倒的な省電力性能で世界に衝撃を与えた。それを実現できた大きな要因の1つとして、当時の最先端技術であるTSMC(台湾積体電路製造)の5nmプロセス「N5」を他社に先行して導入できたことが挙げられる。

このように、デバイス性能で他社を圧倒するには、採用するシリコンの製造を担当する半導体メーカの先進的な技術力が必要不可欠だ。しかし、今では5nmプロセスや4nmプロセスは複数の半導体メーカが製造できるようになってきており、Appleシリコンのプロセス上の優位性は薄れつつある。

そんな中、TSMCの最新の3nm技術「N3」がApple製品に優先的に提供されるとの情報が出回っている。N3は昨年12月末に量産が始まったばかりのTSMCの最新プロセスだが、その性能は予想を超えるものとして高く評価されている。N3はM1シリーズで採用されたN5に対して性能が15%向上し、消費電力が30%低減されるという。

また、ロジック回路の密度が70%向上するとされており、同じサイズであればより多くのトランジスタを搭載できるため、シリコンの性能を一層向上させることが期待されている。そのTSMCのN3の2023年の生産枠の多くが、Appleシリコンの製造に割り当てられる見込みだという。

さらにTSMCは2nmプロセスを含む次世代プロセスのロードマップを発表した。そこからは単なる微細化だけでなく、大きなステップアップとなる新しい技術の導入が計画されている。ここでは、その中から次世代トランジスタ構造「GAA(Gate All Around)」と背面電源供給技術「BPD(Backside Power Delivery)」を紹介する。

次世代トランジスタ構造「GAA」が切り開く微細化技術

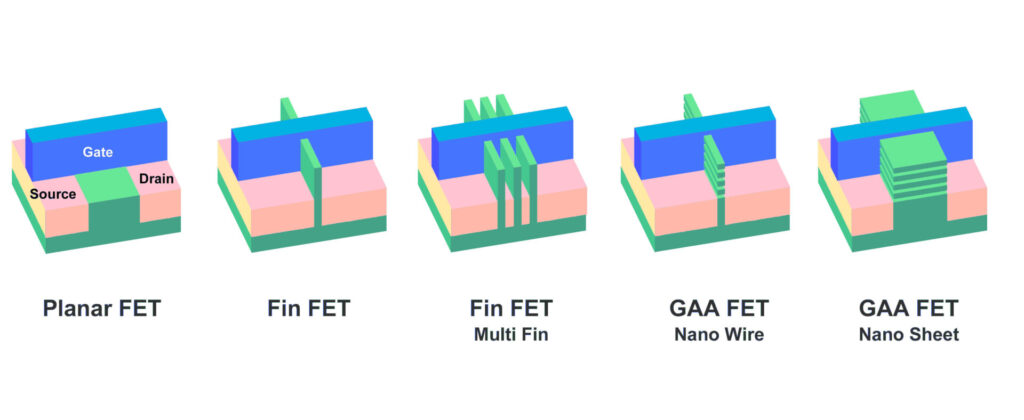

シリコンの微細化ではロジック回路を構成するトランジスタの性能を向上しつつ、そのサイズをいかに小さくできるかが重要だ。2010年以前のシリコンではトランジスタは平面構造の「プレーナ型」と呼ばれる構造が主流だったが、この構造のまま微細化が進むとトランジスタの性能(速度)が低下し、同時にリーク電流(トランジスタがオフ状態の時に漏れる電流のことで本来は無いことが好ましい)が増えて消費電力が下がらない、といった障害が出る。

そこで考案されたのが「FinFET(3Dトランジスタ)」と呼ばれるアプローチで、ロジック動作の要となる「チャネル」を縦に長く伸ばした構造を採った。プレーナ型と同じチャネル面積を確保しつつトランジスタのサイズを縮小でき、さらにリーク電流も低減できることから、微細化の壁を突破する技術として各社の高性能シリコンに相次いで導入された。FinFETはIntelでは「トライゲート」技術と呼ばれ、2012年にリリースされた第3世代Coreプロセッサ「Ivy Bridge」から本格的に採用された。

しかし、微細化が進むと、FinFETでもトランジスタサイズの縮小が難しくなってきた。これは微細化によるトランジスタ性能(動作速度)の向上が困難になったからであり、対策としてFinを複数設ける方法が採られたが、その分トランジスタ面積が大きくなり微細化のメリットが失われる。そこで考案されたのがGAAと呼ばれる技術で、ゲートの接点4面すべてをチャネルとし、これを高さ方向に複数積層することで性能を向上させた。

また、チャネルの幅を広げる(シート化する)ことでさらに性能を向上する「Nanosheet」技術も開発された。Samsungでは、すでに3nmプロセスでGAA技術の導入を先行しており、TSMCでは2nmプロセス(N2)から導入するとしている。またIntelはGAA技術を「RibbonFET」と呼び、2024年に予定されている同社の製造プロセス「Intel 20A」で導入すると発表した。

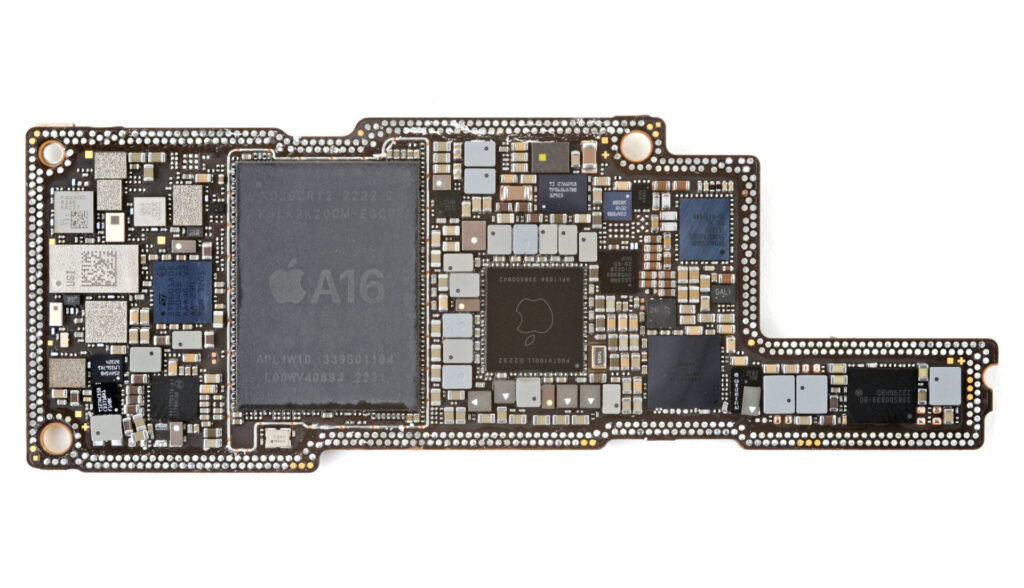

画像⚫︎iFixit

BPD技術が切り拓く次世代シリコンの未来

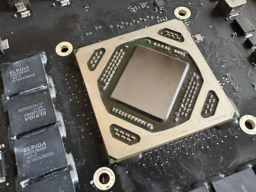

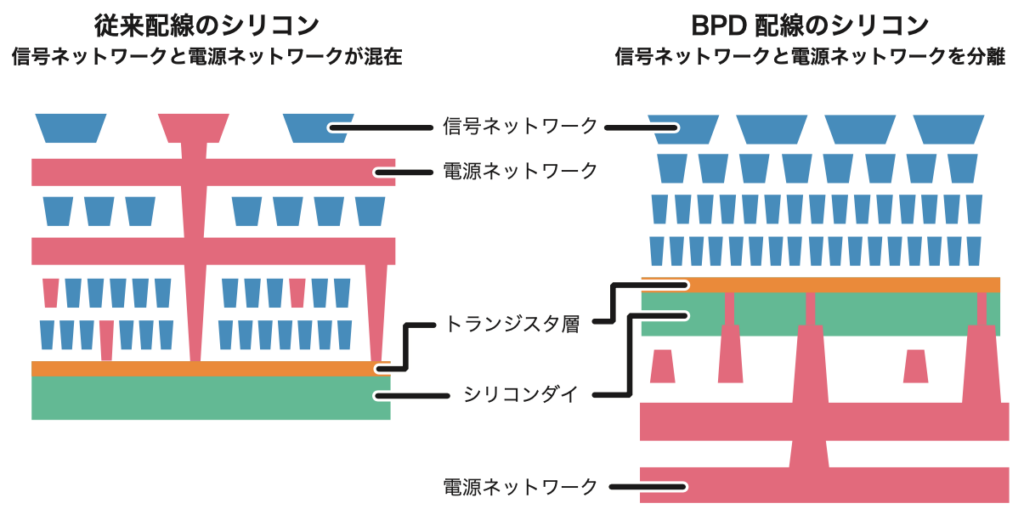

次世代シリコンに向けて導入が検討されているもう1つの技術が、BPDだ。シリコンの微細化では先に述べたようにトランジスタの小型化が重要だが、同時にその上部に積層される配線層の微細化も必要になる。従来は配線の狭ピッチ化と多層化を進めることで微細化に対応してきたが、これらはいずれも配線抵抗の増加につながり、性能低下やエネルギー効率悪化の要因となっていた。

そこでシリコン上部の配線層から信号ネットワークと電力ネットワークを分離し、電力ネットワークのみをシリコンの下部(裏面)に配置する技術がBPDだ。これによってシリコン上部の信号ネットワークの配線密度が下がり、より多くの信号ネットワークをコンパクトに配線することができる。さらに、電力ネットワークから発生するノイズ(雑音)が信号ネットワークに悪影響を及ぼすリスクを大幅に低減でき、信号品質の向上も期待できる。

一方、電力ネットワークはそのサイズや密度の制限から解放されることから、シリコン全体への電源供給能力が大きく改善され、電源品質が大きく向上する。電源配線による電力ロスも大幅に改善が見込まれることから、チップ全体のエネルギー効率と性能向上も期待できるのだ。

IntelはこのBPD技術を「PowerVia」と呼び、「RibbonFET」と同じく「Intel 20A」での導入を見込んでいる。そして、TSMCは少し遅れて2025年に予定される第2世代の2nmプロセス「N2P」でBPD技術を導入すると発表している。

このように次世代シリコンをめぐる新技術の開発競争は激しさを増しており、その成否が半導体メーカの将来はもちろん、Appleをはじめとするデバイスメーカの成功をも左右する重要な要素となっている。Appleシリコンが今後も他社を圧倒するようなパフォーマンスを維持し続けることができるかどうか、それはパートナーに選んだ半導体メーカの戦略に掛かっていると言っても過言ではない。

第2世代5nmプロセス「N5P」を採用するM2シリーズがM2 Ultraの登場によって完結した今、次世代を担う新しいAppleシリコンが、最新の半導体技術の導入によって再び業界をリードする日が待ち遠しい。

著者プロフィール